Les ofrecemos este tutorial I2C en el cual abordamos este apasionante protocolo muy a fondo, aprenderá todo sobre el protocolo de BUS serie I2C a 2 hilos; Qué fácil es de usar, cómo funciona y cuándo usarlo …

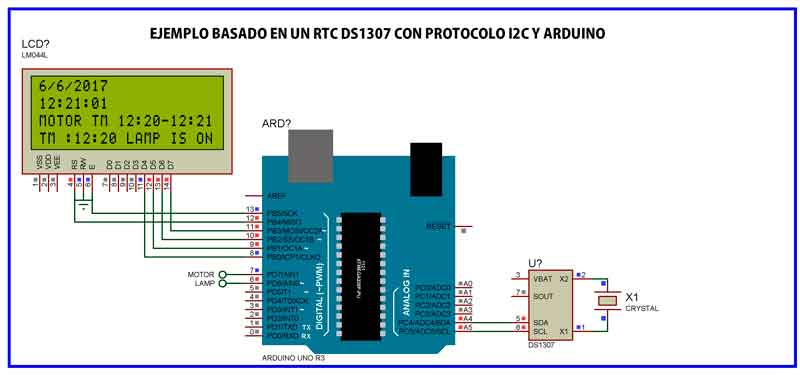

El Protocolo I2C es un protocolo de comunicación serie muy útil desarrollado en 1982 por Philips Semiconductors. Este popular sistema se utiliza en una gran variedad de chips. Algunos ejemplos muy populares incluyen el IC DS1307 (RTC) y DS23017 (expansor en serie). Le permite conectar muchos dispositivos a un solo conjunto de dos cables y luego comunicarse individualmente con cada dispositivo con el que puede enviar y recibir datos.

Todo lo que necesitas saber en este Tutorial I2C

Este tutorial I2C le muestra cómo funciona el protocolo I2C en el nivel de bits físicos sobre el modo maestro único (un solo dispositivo de control) que es el uso más común para I2C en un sistema pequeño.

Advertencia: El protocolo está diseñado para comunicación de placa única, no es un sistema de comunicación de larga distancia. Puede encontrar instancias (historias de terror) de personas que diseñan un sistema de comunicación entre oficinas múltiples con extensiones I2C. Simplemente no lo haga, ¡termina en lágrimas!

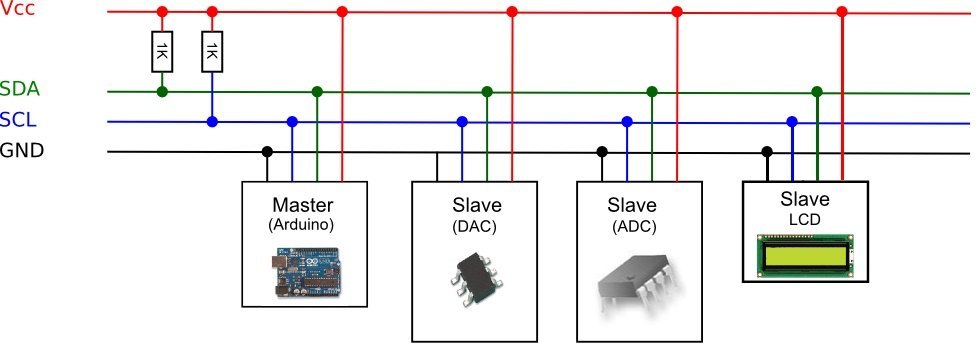

I²C (pronunciado I-squared-C) y comúnmente escrito como ‘I2C’ significa Inter-Integrated Circuit y permite la comunicación de datos entre dispositivos I2C a través de dos cables. Envía información en serie usando una línea para datos (SDA) y una para reloj (SCL).

El otro acrónimo de I2C es IIC (este es en realidad el correcto) y significa «comunicación Inter IC», que muestra que está destinado a la comunicación de chip a chip.

Nota: Puede encontrar rutinas I2C del modo maestro en compiladores de C, Pascal, Basic, etc.

El Maestro y el esclavo

El protocolo phillips I2C define el concepto de dispositivos maestros y esclavos. Un dispositivo maestro es simplemente el dispositivo que está a cargo del bus en este momento y este dispositivo controla el reloj y genera señales START y STOP. Los esclavos simplemente escuchan el bus y actúan sobre los controles y los datos que se envían.

El maestro puede enviar datos a un esclavo o recibir datos de un esclavo: los esclavos no transfieren datos entre ellos.

Modo Multi Maestro

La operación multimaestro es un uso más complejo de I2C que le permite tener diferentes dispositivos de control en el mismo bus. Solo necesita usar este modo si tiene más de un microcontrolador en el bus (y desea que cualquiera de ellos sea el maestro del bus).

La operación multi-master implica el arbitraje del bus (donde un maestro debe luchar para obtener el control del bus) y la sincronización del reloj (cada uno puede usar un reloj diferente, por ejemplo, debido a los relojes de cristal separados para cada micro).

Nota: Multi Master no está cubierto en este tutorial I2C ya que el uso más común de I2C es usar un único bus maestro para controlar dispositivos periféricos, por ejemplo, memoria serie, ADC, RTC, etc.

Datos y reloj

La interfaz I2C utiliza dos líneas bidireccionales, lo que significa que cualquier dispositivo podría conducir cualquiera de las líneas. En un sistema maestro único, el dispositivo maestro acciona el reloj la mayor parte del tiempo: el maestro está a cargo del reloj, pero los esclavos pueden influir en él para desacelerarlo (ver Periféricos lentos a continuación).

Los dos cables deben conducirse como salidas abiertas de colector / drenaje y deben elevarse con una resistencia (es decir, una resistencia por línea I2C, es decir, datos y reloj); esto implementa una ‘función NOR cableada’ – cualquier dispositivo que desconecte el cable hace que todos los dispositivos vean un valor lógico bajo; para un valor lógico alto, todos los dispositivos deben detener el cableado.

Un Bus exclusivo

Nota: Si usa I2C, no puede colocar ningún otro dispositivo (que no sea I2C) en el bus, ya que ambas líneas se utilizan como reloj en algún punto (la generación de bits START y STOP alterna la línea de datos). Por lo tanto, no puede hacer algo inteligente, como mantener la línea del reloj inactiva y utilizar la línea de datos como un botón de detección de presión (para guardar los pines).

El Bus I2C es ampliamente utilizado en la industria del automóvil.

A menudo encontrará dispositivos que se dan cuenta que son compatibles con I2C, pero están etiquetados como «interfaz de 2 hilos». ¡El fabricante evita pagar regalías al no usar las palabras «I2C»!

Hay dos cables (tres si incluye la Masa (GND), y cuatro si también incluye potencia), pero la potencia y la masa se toman como dados, es decir, están disponibles en un pcb según sea necesario, por lo que realmente no cuentan.

Nota: Para un verdadero protocolo de 1 cable alimentado por la línea de señal, consulte el protocolo «One-Wire» (un ejemplo es el DS18B20); este también ignora el cable de retorno a tierra requerido (por lo tanto, es realmente un sistema de cables). Este protocolo proporciona un sistema multidrop de cable largo y de larga distancia, aunque a una velocidad menor que I2C.

Señales de datos

SDA: datos en serie

SCL: reloj en serie

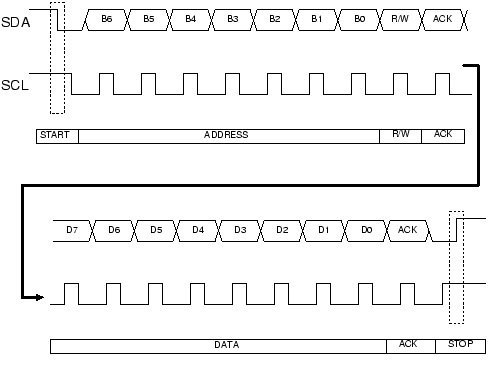

La típica transacción de señalización

Tutorial I2C: señales SDA y SCL típicas

Velocidad del Bus I2C

Las velocidades de reloj estándar son entre 100 kHz y 10 kHz, pero el estándar te permite usar velocidades de reloj de cero a 100 kHz y también está disponible un modo rápido (400 kHz – modo rápido). Una velocidad aún mayor (3.4 MHz – modo de alta velocidad) para aplicaciones más exigentes – ¡El PIC de rango medio aún no estará en este modo!

Nota: El modo de baja velocidad se ha omitido (10kHz) ya que el estándar ahora especifica el sistema básico que opera de 0 a 100kHz.

Nota: Incluso si ejecuta un periférico I2C a alta velocidad, la velocidad total de datos depende de qué tan rápido pueda insertar datos en el modulo I2C interno y eso depende de la velocidad del procesador.

Es posible que un dispositivo esclavo lento detenga el bus mientras reúne datos o servicios, una interrupción, etc. Puede hacerlo mientras mantiene baja la línea de reloj (SCL) forzando al maestro al estado de espera. El maestro debe esperar hasta que se libere SCL antes de continuar.

Secuencia de transferencia de datos

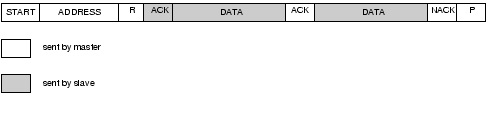

Una secuencia básica de lectura o escritura de maestro a esclavo para I2C sigue el siguiente orden:

I2C Tutorial: secuencia de comandos básicos de I2C.

- 1. Enviar el bit START (S).

- 2. Enviar la dirección del esclavo (ADDR).

- 3. Envíe el bit de Lectura (R) -1 / Escritura (W) -0.

- 4. Espere / envíe un bit de confirmación (A).

- 5. Enviar / recibir el byte de datos (8 bits) (DATA).

- 6. Espere / envíe el bit de confirmación (A).

- 7. Enviar el bit STOP (P).

I2C Tutorial: final de la secuencia de comandos básicos de I2C.

Nota: Puede usar direcciones de 7 bit o 10 bit.

La secuencia 5 y 6 puede repetirse para que un bloque multibyte pueda leerse o escribirse.

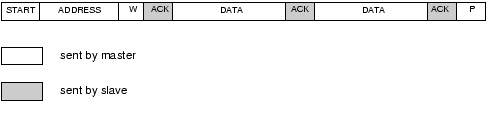

Transferencia de datos de maestro a esclavo

Tutorial I2C: datos de secuencia de instrucciones del maestro al esclavo

Un dispositivo maestro envía la secuencia S ADDR W y luego espera un bit de confirmación (A) del esclavo que el esclavo solo generará si su dirección interna coincide con el valor enviado por el maestro. Si esto sucede, el maestro envía DATA y espera el reconocimiento (A) del esclavo. El maestro completa la transferencia de bytes generando un bit de parada (P) (o inicio repetido).

Transferencia de datos de esclavo a maestro

Tutorial I2C: datos de secuencia de instrucciones de esclavo a maestro

Un proceso similar ocurre cuando un maestro lee desde el esclavo, pero en este caso, en lugar de W, se envía R. Después de que los datos se transmiten del esclavo al maestro, el maestro envía el acuse de recibo (A). Si, en cambio, el maestro no quiere más datos, debe enviar un mensaje de no confirmación que indique al esclavo que debería liberar el bus. Esto permite que el maestro envíe el STOP o la señal de START repetido.

Direcciones del dispositivo

Cada dispositivo que utilice en el bus I2C debe tener una dirección única. Para algunos dispositivos, por ejemplo, la memoria en serie, puede configurar los bits de dirección más bajos usando pines de entrada en el dispositivo, otros tienen una configuración de dirección interna fija, por ejemplo, un reloj de tiempo real DS1307. Puede poner varios dispositivos de memoria en el mismo bus IC usando una dirección diferente para cada uno.

Cada fabricante de dispositivos tiene asignado un conjunto de direcciones para que los dispositivos no entren en conflicto entre sí.

Nota: El número máximo de dispositivos está limitado por la cantidad de direcciones disponibles (y necesita direcciones que no sean conflictivas) y por la capacidad total del bus (máximo 400 pF).

Llamada general

La dirección de llamada general es una dirección reservada que, cuando se envía por el maestro del bus, debe dirigirse a todos los dispositivos que deben responder con un acuse de recibo. Su valor es 0000000 (7 bits) y está escrito por el maestro 0000000W. Si un dispositivo no necesita datos de la llamada general, no necesita responder.

Tutorial I2C: direcciones reservadas.

0000 000 1 Byte START – para micros lentos sin I2C h / w

0000 001 X Dirección CBUS – un protocolo de bus diferente

0000 010 X Reservado para diferentes formatos de bus

0000 011 X Reservado para propósitos futuros

0000 1XX X Código maestro Hs-mode

1111 1XX X Reservado para propósitos futuros

1111 0XX X direccionamiento de esclavo de 10 bits

Fin de las direcciones reservadas.

La mayoría de estos no son tan útiles para los microcontroladores PIC, excepto tal vez el byte START y el direccionamiento de 10 bits.

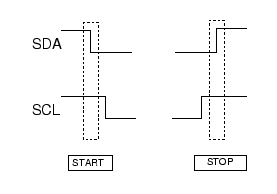

START (S) y STOP (P) bits

Los bits START (S) y STOP (P) son señales únicas que se pueden generar en el bus pero solo por un maestro de bus.

La recepción de un bit START por un dispositivo esclavo I2C restablece su lógica de bus interno. Esto se puede hacer en cualquier momento para que pueda forzar el reinicio si algo sale mal incluso en el medio de la comunicación.

Los bits START y STOP se definen como flancos ascendentes o descendentes en la línea de datos mientras la línea del reloj se mantiene alta.

Tutorial I2C: definición de texto de señales START y STOP

| START condition (S) | SCL = 1, SDA falling edge |

| STOP condition (P) | SCL = 1, SDA rising edge |

Fin de la definición de texto de las señales START y STOP

El siguiente diagrama muestra gráficamente la información anterior: estas son las señales que vería en el bus I2C.

START (S) y STOP (P) bits.

Fin de la definición de señales START y STOP

Nota: En un sistema maestro único, la única diferencia entre un esclavo y un maestro es la capacidad del maestro de generar bits de ARRANQUE y DETENCIÓN. Tanto el esclavo como el maestro pueden controlar SDA y SCL.

Repetido INICIO

Esto parece un término confuso al principio cuando te preguntas por qué molestarse con él, ya que es funcionalmente idéntico a la secuencia:

S ADDR (R / W) DATA AP

La única diferencia es que para un inicio repetido puede repetir la secuencia comenzando desde el bit de parada (reemplazando el bit de parada con otro bit de inicio).

S ADDR (R / W) DATOS A Sr ADDR (R / W) DATA AP

y puedes hacer esto indefinidamente

Nota: La recepción de S o Sr obliga a cualquier dispositivo I2C a reiniciar su lógica de bus interno, por lo que enviar S o Sr realmente restablece todos los dispositivos de bus. Esto se puede hacer en cualquier momento , es un restablecimiento forzado.

La razón principal por la que existe el bit Sr está en una configuración de múltiples maestros donde el maestro de bus actual no desea liberar su maestría. Usar el inicio repetido mantiene ocupado el bus para que ningún otro maestro pueda tomar el bus.

Debido a esto, cuando se usa en una configuración maestra única, es solo una curiosidad.

Datos

Todos los bloques de datos están compuestos de 8 bits. El bloque inicial tiene 7 bits de dirección seguidos de un bit de dirección (lectura o escritura). Los siguientes bloques tienen 8 bits de datos. Los bits de acuse de recibo están comprimidos entre cada bloque.

Cada byte de datos se transmite primero a MSB, incluido el byte de dirección.

Para permitir la generación de bit START y STOP mediante el maestro, la línea de datos (SDA) no debe cambiarse mientras el reloj (SCL) está alto; solo se puede cambiar cuando el reloj está bajo.

Reconocer

El bit de confirmación (generado por el dispositivo receptor) indica al transmisor que la transferencia de datos fue correcta. Tenga en cuenta que el pulso de reloj para el bit de confirmación siempre lo crea el maestro de bus.

El bit de confirmación de datos es generado por el maestro o esclavo dependiendo de la dirección de los datos. Para el maestro que escribe a un esclavo (W), el esclavo genera el reconocimiento. Para el maestro que recibe datos (R) de un esclavo, el maestro genera el bit de confirmación.

Tutorial I2C: Definición de bits de ACK

| Reconocer | 0 voltios |

| No reconocer | Alto voltaje |

Fin de la definición de bits de ACK

Maestro de datos ACK -> esclavo

En este caso, el esclavo genera la señal de confirmación.

Cuando el maestro de bus recibe un mensaje de no confirmación, la transferencia ha fallado y el maestro debe generar un PARO o inicio repetido para abortar la secuencia.

ACK esclavo de datos -> maestro

En este caso, el maestro genera la señal de confirmación.

Normalmente, el maestro generará un acuse de recibo después de haber recibido los datos, pero para indicar al esclavo que no se requieren más datos en la última transferencia de bytes, el maestro debe generar un «no reconocimiento». Esto le indica al esclavo que debería dejar de enviar datos. El maestro puede generar el bit STOP (o START repetido).

Llamada general

La función de llamada general es un comando especializado que debe ser aceptado por todos los dispositivos en el bus. Permite que un dispositivo maestro se comunique con todos los dispositivos al mismo tiempo, proporcionándoles algunos datos. Tal vez usaría esto para ordenar un restablecimiento de software en el caso de un tiempo de espera de vigilancia en el procesador.

Tutorial I2C: detalles para el 16F88

Configuración de pines

Para usar el modo I2C en el 16F88, los pines SDA y SCL deben inicializarse como entradas (bit TRIS = 1) para que se cree un efecto de drenaje abierto. Al configurarlos como entradas, no están manejando los cables y una resistencia de extracción externa hará que las señales sean altas.

16F88 en Modo esclavo

El 16F88 implementa completamente todas las funciones esclavas excepto la llamada general.

- Modo esclavo completo

La función de llamada general en realidad no importa, ya que es bastante especializada y ordena a todos los dispositivos del bus que utilicen algunos datos.

Se genera una salida baja conduciendo la línea de señal baja y cambiando la dirección del pin a una salida. Se genera una salida alta al cambiar la dirección del pin a una entrada, de modo que la resistencia externa tire de la señal hacia arriba.

En modo esclavo, esta acción la realiza el módulo SSP (las salidas del registro en SDA y SCL se reducen automáticamente, independientemente del estado del valor de registro).

Modo maestro del 16F88

Básicamente, la funcionalidad del modo maestro es muy limitada.

Hay dos elementos que se proporcionan:

- Interrupciones

- Control de pin

Las interrupciones del 16F88

Hay dos interrupciones que se activan al recibir una condición de START o STOP. Estas dos interrupciones solo son útiles en un sistema de modo maestro múltiple donde es necesario que el dispositivo no maestro detecte las condiciones de inicio y parada. ¡Entonces, para un solo sistema maestro, no sirven para nada!

Pin de Control del 16F88

Nota Cuando el módulo SSP está activo, las salidas SDA y SCL siempre se configuran en cero independientemente del estado de los valores de registro. Entonces, todo lo que tienes que hacer es controlar la dirección del puerto.

En el modo maestro (16F88), SDA y SCL deben controlarse con el software.

A fondo, Tutorial I2C: detalles para el Chip 16F877A

¡Lo hace todo por ti!

- Modo maestro completo.

- Modo esclavo completo.

- Llamada general completa.

Nota: Si desea un chip con funcionamiento de modo maestro y esclavo completo, busque el módulo MSSP en un chip PIC, por ejemplo, 16F877A, entonces no necesitará más software, solo lo suficiente para manejar el módulo.

Referencia: best-microcontroller-projects

Ejemplos de proyectos con PIC y AVR

En otro capítulo le añadiremos ejemplos de proyectos con el protocolo I2C.

Comenten amigos y si tienen algún proyecto con este protocolo, nos lo envía y se lo publicaremos.